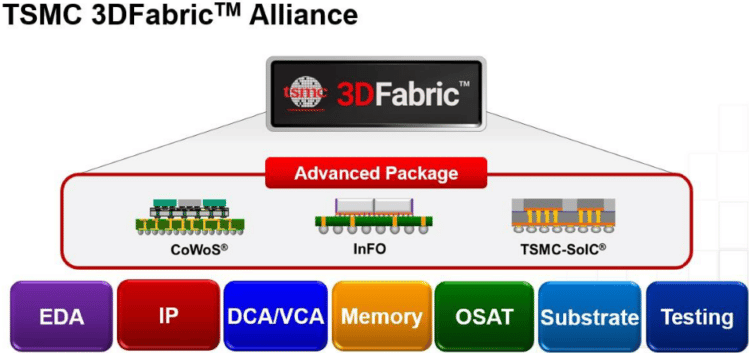

台积电近日于该公司的2022开放创新平台生态系统论坛上宣布,将成立开放创新平台(OIP) 3DFabric联盟。此崭新的3DFabric联盟是台积公司的第六个OIP联盟,也是半导体产业中第一个与合作伙伴携手加速创新及完备三维积体电路(3D IC)生态系统的联盟,提供最佳的全方位解决方案与服务以支援半导体设计、记忆体模组、基板技术、测试、製造及封装。此联盟将协助客户达成晶片及系统级创新的快速实作,并且採用台积公司由完整的3D硅堆叠与先进封装技术系列构成的3DFabric技术来实现次世代的高效能运算及行动应用。

台积电宣布成立第六个OIP生态系相关联盟,加强推动3D IC发展进程

台积科技院士/设计暨技术平台副总经理鲁立忠博士表示,3D晶片堆叠及先进封装技术为晶片级与系统级创新开启了一个新时代,同时也需要广泛的生态系统合作,以协助设计人员透过各种选择及方法寻找出最佳途径。在台积电与生态系统合作伙伴共同引领之下,3DFabric联盟为客户提供了简单且灵活的方式,为其设计释放3D IC的力量。

超微半导体公司(AMD)技术及产品工程资深副总裁Mark Fuselier表示,作为小晶片(Chiplet)及3D晶片堆叠的先驱者,AMD对于台积电3DFabric联盟的成立,及其在加速系统级创新方面将扮演的重要角色感到期待。AMD已经见证了与台积电及其OIP伙伴合作开发全球首颗以系统整合晶片(TSMC-SoIC)为基础的中央处理器的好处,期待透过更紧密的合作,来推动坚实的Chiplet堆叠生态系统发展,以支援未来世代具备节能效益及高效能优势的晶片。

六大联盟共组OIP生态系

作为业界最完备且最有活力的生态系统,台积电OIP由六个联盟组成:电子设计自动化(EDA)联盟、硅智财(IP)联盟、设计中心联盟(DCA)、价值链联盟(VCA)、云端联盟,以及最新成立的3DFabric联盟。台积公司于2008年成立开放创新平台,藉由建立新的合作模式,组织台积公司技术、EDA、IP和设计方法的开发及最佳化,来协助客户克服複杂半导体设计带来的日益严峻挑战。

新成立的3DFabric联盟成员能够及早取得台积公司的3DFabric技术,使得他们能够与台积公司同步开发及最佳化解决方案,也让客户在产品开发方面处于领先地位,及早获得从EDA及IP到DCA/VCA、记忆体、委外封装测试(OSAT)、基板及测试的最高品质与既有的解决方案及服务。

与3DFabric联盟伙伴的崭新合作

• EDA伙伴能够及早取得台积公司的3DFabric技术来进行EDA工具开发与升级,提供最佳化的EDA工具及设计流程,进而提升3D IC设计的效率。

• IP伙伴开发符合晶片对晶片介面标准及台积公司3DFabric技术的3D IC硅智财,为客户提供各种最高品质且经过验证的IP解决方案。

• DCA/VCA伙伴在3DFabric技术方面及早与共同客户合作,并与台积电达成路线图的共识,进而提升其3DFabric设计、IP整合及生产的服务能力。

• 记忆体伙伴与台积电及早进行技术合作,定义规格并及早与台积电协调工程和技术标准,这将缩短未来高频宽记忆体世代产品的上市时间,以满足3D IC设计的要求。

• 支援台积电生产品质及技术要求的OSAT伙伴,藉由持续改善各种技术和生产支援,与台积公司携手合作满足客户的生产需求。

• 基板伙伴与台积电及早进行技术合作与开发,以满足3DFabric技术的未来要求,这将提升基板材料的品质、可靠性及新基板的整合性,加速客户3D IC设计的生产。

• 测试伙伴及早与台积电合作,为台积公司的3DFabric技术开发测试与压力研究方法,提供完备的可靠性及品质要求,协助客户快速推出具有差异化的产品。

NVIDIA先进技术事业群资深副总裁Joe Greco指出,NVIDIA採用台积电的CoWoS技术及支援架构,生产了数个世代的高效能GPU产品。全新的3DFabric联盟将把这项技术扩展至更广泛的产品面及更高程度的整合。

以3Dblox实现3D IC设计流程标准化

为了克服日益複杂的3D IC设计,台积电推出了3Dblox标准,将设计生态系统与经由验证的EDA工具与流程加以结合,以支援台积电的3DFabric技术。模组化的3Dblox标准旨在以单一格式制定3D IC设计中的关键物理堆叠及逻辑连接资讯。台积电已与3DFabric联盟中的EDA伙伴合作,让3Dblox全面适用于3D IC设计,包括物理实作、时序验证、物理验证、电迁移IR压降(EMIR)分析、热分析等。台积公司3Dblox的目的在于将灵活性与易用性最大化,提供最佳的3D IC设计生产力。

2721

2721

下载ECAD模型

下载ECAD模型