1. 概述

NXP i.MX93处理器有两个以太网控制器,其中eqos是TSN网络控制器。另外一个Fec以太网外围设备使设备能够在以太网上传输和接收符合IEEE 802.3-2002标准的数据,提供了一个可配置的、灵活的外设,以满足各种应用程序和客户的需求。一般情况CPU集成MAC,PHY采用独立芯片;CPU不集成MAC,MAC和PHY采用集成芯片。MAC和PHY工作在OSI模型的数据链路层和物理层。i.MX93的MAC集成在CPU内部,所以还需要外接PHY芯片。

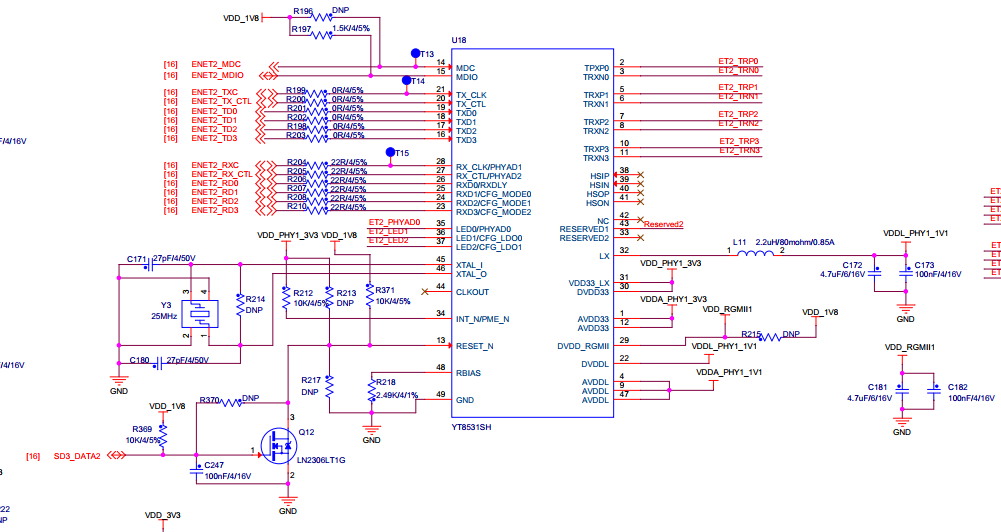

MYD-LMX9X开发板外接了两个YT8531SH千兆PHY芯片,ENET1原理图如图1-1:

图1-1. ENET1原理图

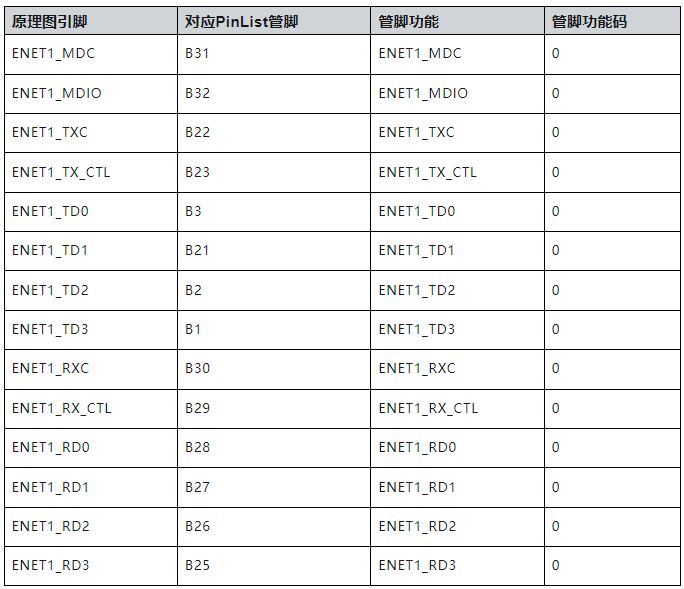

查看原理图与《MYD-LMX9X-PinList-V1.0.pdf》得出 ENET1数据管脚与i.MX93的对应关系如表1-2:

表1-2. ENET1引脚对应关系

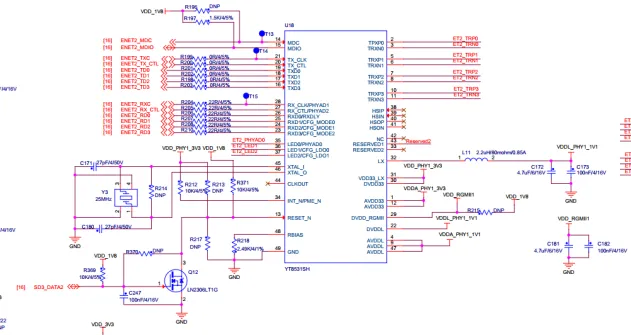

图1-3. ENET2原理图

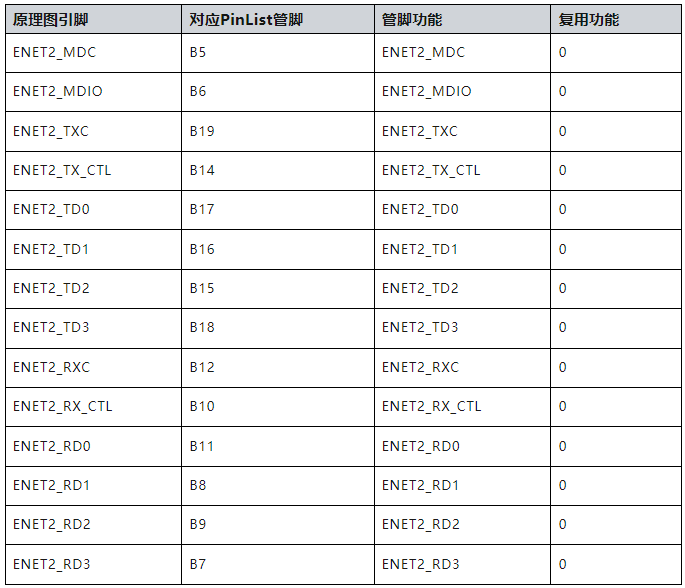

查看原理图与《MYD-LMX9X-PinList-V1.0.pdf》得出 ENET2数据管脚与MYD-LMX9X的对应关系如表1-4:

表1-4. ENET2引脚对应关系

2. 网卡驱动移植

2-1. 查看内核设备引脚定义

在内核中,有对i.MX93芯片的网口设备树资源做了定义,此部分由芯片产商提供,属于公共资源,实际上我们不需要修改这部分,只需要引用即可,如下:

PC:~/myd-lmx9x-bsp/myir-imx-linux$ cat arch/arm64/boot/dts/myir/imx93.dtsi

......

fec: ethernet@42890000 {

compatible = "fsl,imx93-fec", "fsl,imx8mp-fec", "fsl,imx8mq-fec";

reg = <0x42890000 0x10000>;

interrupts = <GIC_SPI 179 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 180 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 181 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 182 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&clk IMX93_CLK_ENET1_GATE>,

<&clk IMX93_CLK_ENET1_GATE>,

<&clk IMX93_CLK_ENET_TIMER1>,

<&clk IMX93_CLK_ENET_REF>,

<&clk IMX93_CLK_ENET_REF_PHY>;

clock-names = "ipg", "ahb", "ptp",

"enet_clk_ref", "enet_out";

assigned-clocks = <&clk IMX93_CLK_ENET_TIMER1>,

<&clk IMX93_CLK_ENET_REF>,

<&clk IMX93_CLK_ENET_REF_PHY>;

assigned-clock-parents = <&clk IMX93_CLK_SYS_PLL_PFD1_DIV2>,

<&clk IMX93_CLK_SYS_PLL_PFD0_DIV2>,

<&clk IMX93_CLK_SYS_PLL_PFD1_DIV2>;

assigned-clock-rates = <100000000>, <250000000>, <50000000>;

fsl,num-tx-queues = <3>;

fsl,num-rx-queues = <3>;

fsl,stop-mode = <&wakeupmix_gpr 0x0c 1>;

status = "disabled";

};

eqos: ethernet@428a0000 {

compatible = "nxp,imx93-dwmac-eqos", "snps,dwmac-5.10a";

reg = <0x428a0000 0x10000>;

interrupts = <GIC_SPI 183 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 184 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "eth_wake_irq", "macirq";

clocks = <&clk IMX93_CLK_ENET_QOS_GATE>,

<&clk IMX93_CLK_ENET_QOS_GATE>,

<&clk IMX93_CLK_ENET_TIMER2>,

<&clk IMX93_CLK_ENET>,

<&clk IMX93_CLK_ENET_QOS_GATE>;

clock-names = "stmmaceth", "pclk", "ptp_ref", "tx", "mem";

assigned-clocks = <&clk IMX93_CLK_ENET_TIMER2>,

<&clk IMX93_CLK_ENET>;

assigned-clock-parents = <&clk IMX93_CLK_SYS_PLL_PFD1_DIV2>,

<&clk IMX93_CLK_SYS_PLL_PFD0_DIV2>;

assigned-clock-rates = <100000000>, <250000000>;

intf_mode = <&wakeupmix_gpr 0x28>;

clk_csr = <0>;

nvmem-cells = <ð_mac2>;

nvmem-cell-names = "mac-address";

status = "disabled";

};

上述只是对网口做了基本的初始化,并没有对具体的硬件设备进行适配,在实际的情况下需要对具体的网口设备进行硬件引脚资源的适配。

2-2. 添加网卡设备树节点

根据原理图的定义添加网口的设备树配置,修改myir-imx93-11x11.dts文件,如下:

PC:~/myd-lmx9x-bsp/myir-imx-linux$ cat arch/arm64/boot/dts/myir/myir-imx93-11x11.dts

......

&eqos {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_eqos>;

phy-mode = "rgmii-id";

phy-handle = <ðphy1>;

status = "okay";

mdio {

compatible = "snps,dwmac-mdio";

#address-cells = <1>;

#size-cells = <0>;

clock-frequency = <5000000>;

ethphy1: ethernet-phy@1 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <4>;

eee-broken-1000t;

};

};

};

&fec {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_fec>;

phy-mode = "rgmii-id";

phy-handle = <ðphy2>;

fsl,magic-packet;

status = "okay";

mdio {

compatible = "snps,dwmac-mdio";

#address-cells = <1>;

#size-cells = <0>;

clock-frequency = <5000000>;

ethphy2: ethernet-phy@2 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <6>;

eee-broken-1000t;

};

};

};

2-3. 网卡设备数配置

添加网卡设备树节点的eth1_pins和eth2_pins引脚定义:

pinctrl_eqos: eqosgrp {

fsl,pins = <

MX93_PAD_ENET1_MDC__ENET_QOS_MDC 0x57e

MX93_PAD_ENET1_MDIO__ENET_QOS_MDIO 0x57e

MX93_PAD_ENET1_RD0__ENET_QOS_RGMII_RD0 0x57e

MX93_PAD_ENET1_RD1__ENET_QOS_RGMII_RD1 0x57e

MX93_PAD_ENET1_RD2__ENET_QOS_RGMII_RD2 0x57e

MX93_PAD_ENET1_RD3__ENET_QOS_RGMII_RD3 0x57e

MX93_PAD_ENET1_RXC__CCM_ENET_QOS_CLOCK_GENERATE_RX_CLK 0x5fe

MX93_PAD_ENET1_RX_CTL__ENET_QOS_RGMII_RX_CTL 0x57e

MX93_PAD_ENET1_TD0__ENET_QOS_RGMII_TD0 0x57e

MX93_PAD_ENET1_TD1__ENET_QOS_RGMII_TD1 0x57e

MX93_PAD_ENET1_TD2__ENET_QOS_RGMII_TD2 0x57e

MX93_PAD_ENET1_TD3__ENET_QOS_RGMII_TD3 0x57e

MX93_PAD_ENET1_TXC__CCM_ENET_QOS_CLOCK_GENERATE_TX_CLK 0x5fe

MX93_PAD_ENET1_TX_CTL__ENET_QOS_RGMII_TX_CTL 0x57e

>;

};

pinctrl_fec: fecgrp {

fsl,pins = <

MX93_PAD_ENET2_MDC__ENET1_MDC 0x57e

MX93_PAD_ENET2_MDIO__ENET1_MDIO 0x57e

MX93_PAD_ENET2_RD0__ENET1_RGMII_RD0 0x57e

MX93_PAD_ENET2_RD1__ENET1_RGMII_RD1 0x57e

MX93_PAD_ENET2_RD2__ENET1_RGMII_RD2 0x57e

MX93_PAD_ENET2_RD3__ENET1_RGMII_RD3 0x57e

MX93_PAD_ENET2_RXC__ENET1_RGMII_RXC 0x5fe

MX93_PAD_ENET2_RX_CTL__ENET1_RGMII_RX_CTL 0x57e

MX93_PAD_ENET2_TD0__ENET1_RGMII_TD0 0x57e

MX93_PAD_ENET2_TD1__ENET1_RGMII_TD1 0x57e

MX93_PAD_ENET2_TD2__ENET1_RGMII_TD2 0x57e

MX93_PAD_ENET2_TD3__ENET1_RGMII_TD3 0x57e

MX93_PAD_ENET2_TXC__ENET1_RGMII_TXC 0x5fe

MX93_PAD_ENET2_TX_CTL__ENET1_RGMII_TX_CTL 0x57e

>;

};

2-4. 配置内核

PHY驱动位于drivers/net/phy/motorcomm.c,我们只需要把这个驱动打开,编译进内核即可,内核已默认配置网卡驱动,这里我们不再描述。最后编译内核源码,把新生成的设备树dtb文件更新到板子即可。

2-5. 网络测试

- 测试ENET1

root@myd-lmx9x:/# ping www.baidu.com -I eth0

PING www.baidu.com (14.215.177.39): 56 data bytes

64 bytes from 14.215.177.39: seq=0 ttl=56 time=7.987 ms

64 bytes from 14.215.177.39: seq=1 ttl=56 time=8.030 ms

64 bytes from 14.215.177.39: seq=2 ttl=56 time=7.250 ms

- 测试ENET2

root@myd-lmx9x:/# ping www.baidu.com -I eth1

PING www.baidu.com (14.215.177.39): 56 data bytes

64 bytes from 14.215.177.39: seq=3 ttl=56 time=7.507 ms

64 bytes from 14.215.177.39: seq=4 ttl=56 time=7.488 ms

64 bytes from 14.215.177.39: seq=5 ttl=56 time=7.151 ms

64 bytes from 14.215.177.39: seq=6 ttl=56 time=7.043 ms

器件型号:AD9517-4ABCPZ

器件型号:AD9517-4ABCPZ

器件型号:SN74LV595ARGYR

器件型号:SN74LV595ARGYR

下载ECAD模型

下载ECAD模型